Signal Integrity | Analog Mixed Signal Design

| Schematic | SPICE | Physical Design | Verification | Parasitic Extraction | Signal Integrity |

In deep sub-micron technology, interconnect delays and the impact of crosstalk due to parasitic coupling have exceeded gate delays in becoming the main concerns of IC designers on circuit functionality and performance. Zeni SI is a fast and precise signal integrity tool dealing with signal delay analysis, noise analysis and RC reduction.

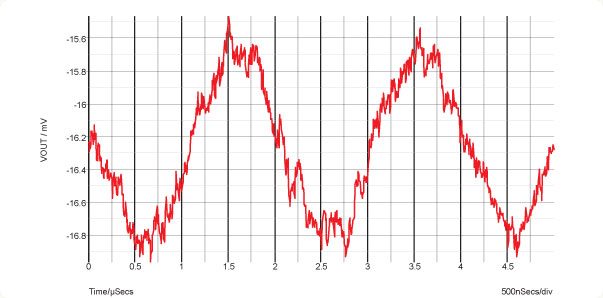

By implementing S-domain analysis and Block Arnoldi method, Zeni SI gains outstanding signal integrity, delay and noise analysis capability over linear interconnect circuit. Its runtime is at least one-order of magnitude faster than traditional simulators, and the result is very close to that of HSPICE.

Zeni SI is easy to use and fully integrated with Zeni PDT. Designers can perform signal integrity, delay and noise analysis with Zeni SI directly by selecting critical nets in the layout editor and interactively finishing parasitic extraction.

For the user's convenience, Zeni SI will back-annotate analysis results onto corresponding schematics and layouts, and generate an output file in standard SDF format in the work directory.

Zeni SI also supports RC reduction for SPICE netlists and results coming from Zeni PE. Its reduction rate can be up to 80%. Zeni SI's RC reduction can achieve higher accuracy since it is based on frequency and error percentage rather than absolute value. HSPICE simulation results of reduced netlists are very close to those of original netlists, while the runtime is much shorter.

Email us with any other questions you may have: info(at)zeni-eda.com